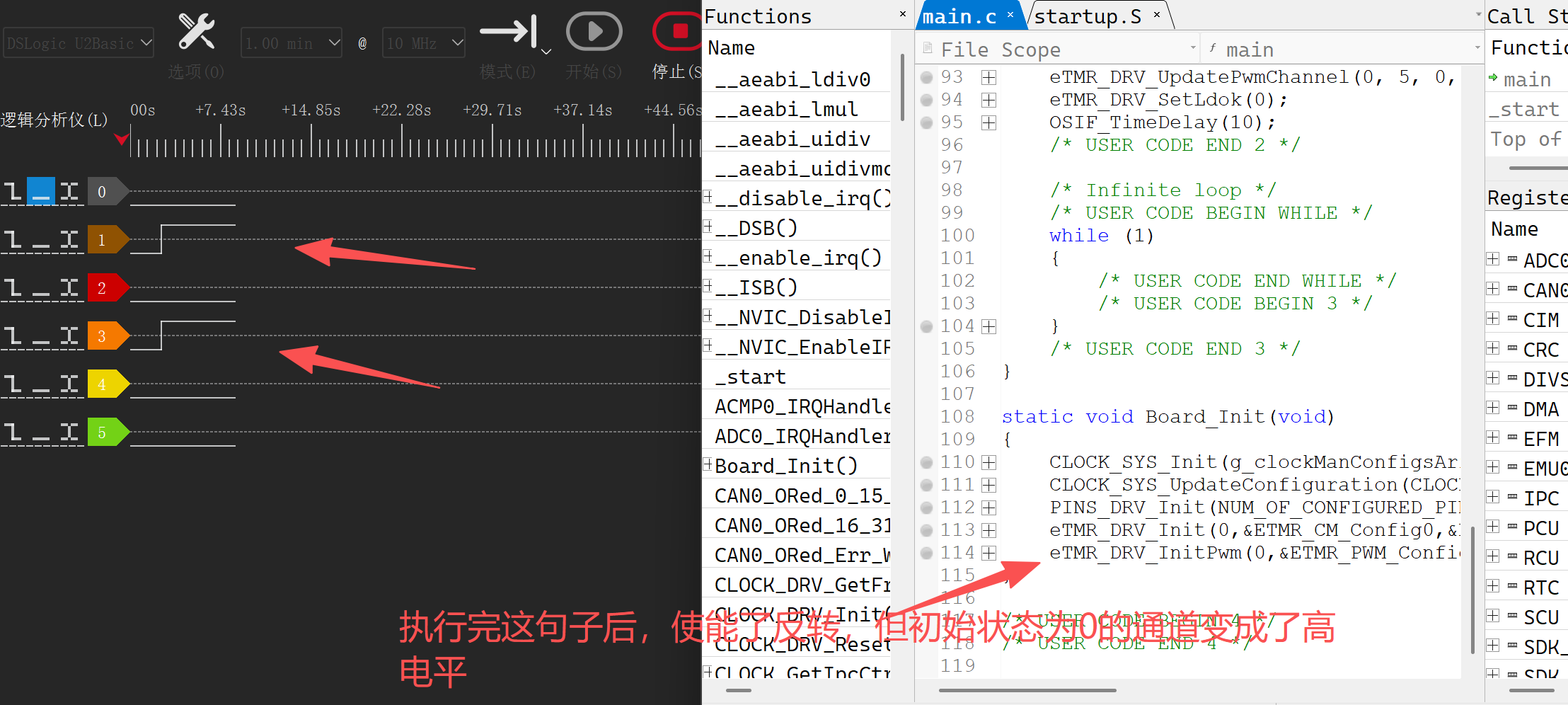

Z1LS0 etmr 配置“Polarity of the channel PWM signal”后通道初始状态异常

-

Etmr_Pwm_Demo_0105.zip这是我的工程

-

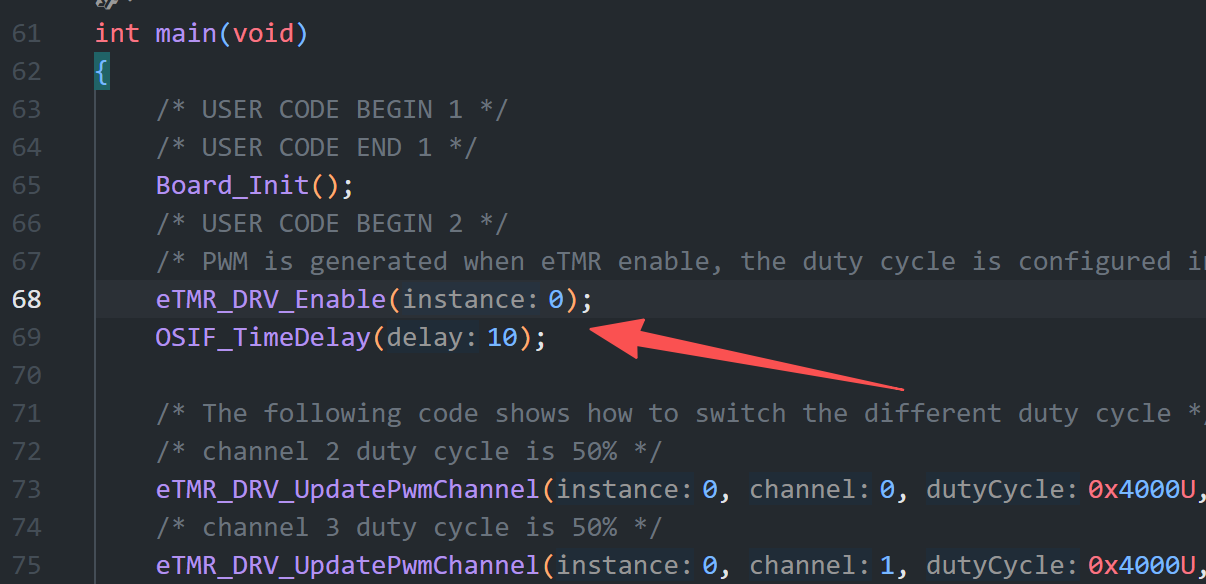

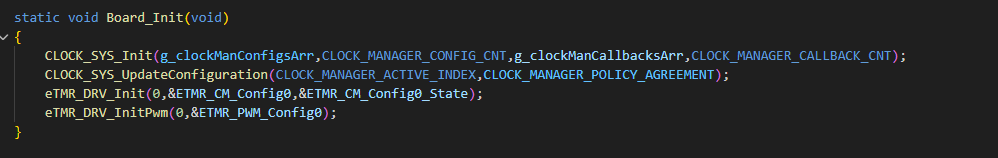

SSEZKX 是指初始化顺序要这样配置么:

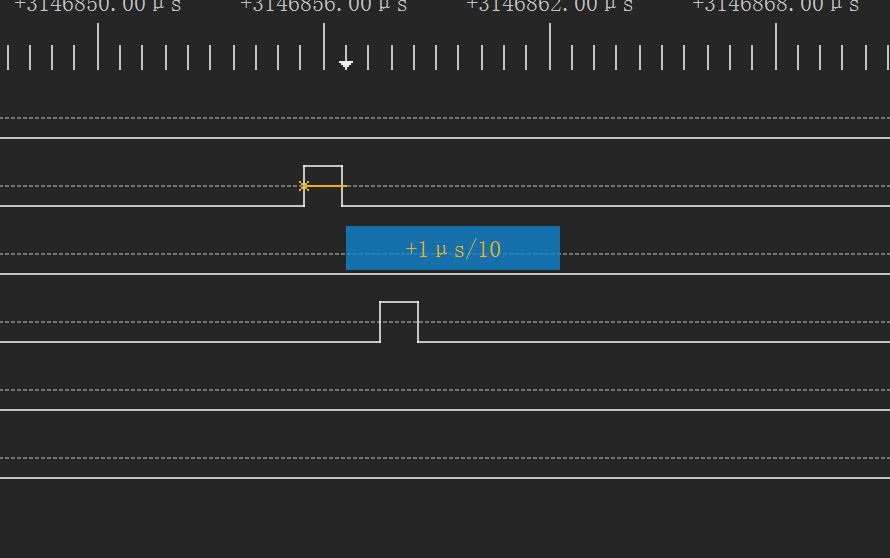

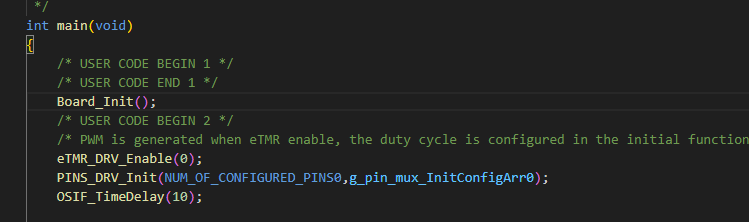

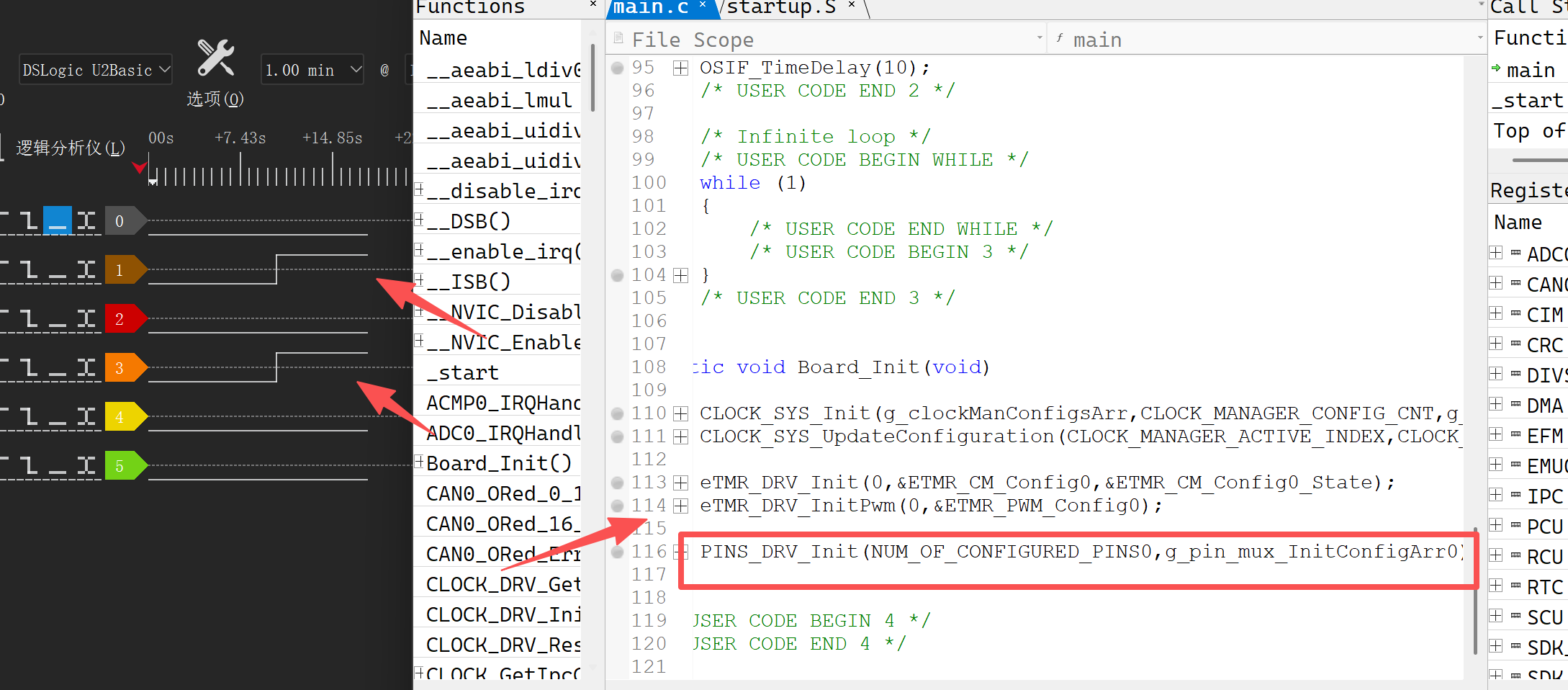

CLOCK_SYS_Init(g_clockManConfigsArr,CLOCK_MANAGER_CONFIG_CNT,g_clockManCallbacksArr,CLOCK_MANAGER_CALLBACK_CNT); CLOCK_SYS_UpdateConfiguration(CLOCK_MANAGER_ACTIVE_INDEX,CLOCK_MANAGER_POLICY_AGREEMENT); eTMR_DRV_Init(0,&ETMR_CM_Config0,&ETMR_CM_Config0_State); eTMR_DRV_InitPwm(0,&ETMR_PWM_Config0); PINS_DRV_Init(NUM_OF_CONFIGURED_PINS0,g_pin_mux_InitConfigArr0);现象还是跟之前一样,执行完eTMR_DRV_InitPwm(0,&ETMR_PWM_Config0); 后,初始状态为0的通道在勾选“Polarity of the channel PWM signal”的情况下,实际输出为高电平

快速上手云途开发生态

发帖前请查看

帮助改进和优化YT CONFIG TOOL,有机会抽取YTM32B1ME0 EVB哦...