YTM32B1LE0 IIS

-

50us的时间间隔由以下主要的时间组成(建议把PCS的信号线引出观察PCS的高低才是决定一个帧的开始或者结束)

- SCK结束到PCS拉起的时间(这里主要会导致您贴的示波器途中SCK和TMU trigger之间的距离),缩短方式SPI_CLK_SCKPCS(x)

- TMU trigger后产生后到下一帧开始的时间主要由:帧间隔时间(和代码执行时间相重合,哪个时间长是哪个)/代码执行时间+PCS拉低到SCK开始的时间(用SPI_CLK_PCSSCK(x)缩短时间);

- 当然,调节以上方式都是在不影响一包数据中的帧间隔,即在一包数据的帧与帧之间的间隔时间(SCKPCS + FMDLY + PCSSCK)基本等于1bit时间才能保证不失真。

注意:请问下是否只有一包的最后一帧才会出现TMU由严重的延时

快速上手云途开发生态

发帖前请查看

帮助改进和优化YT CONFIG TOOL,有机会抽取YTM32B1ME0 EVB哦...

这个是通过硬件响应配置的spi发送开始和结束时tum进行反转。似乎反应也不是很及时,我们需要输出一个连续且标准的正弦波,这个时间能不能调整让信号对其,让iis正常工作这个程序是直接放在循环里去跑的。

这个是通过硬件响应配置的spi发送开始和结束时tum进行反转。似乎反应也不是很及时,我们需要输出一个连续且标准的正弦波,这个时间能不能调整让信号对其,让iis正常工作这个程序是直接放在循环里去跑的。

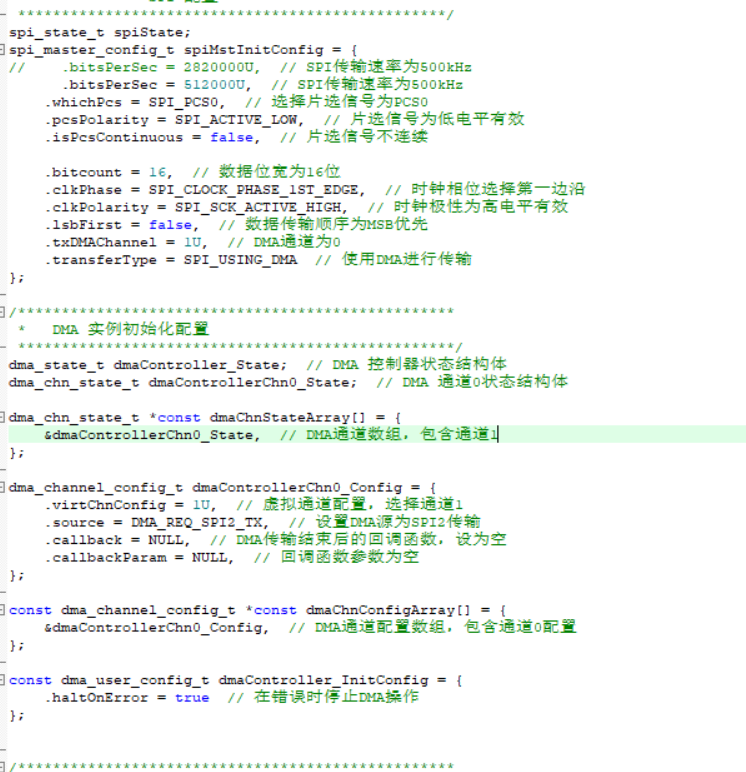

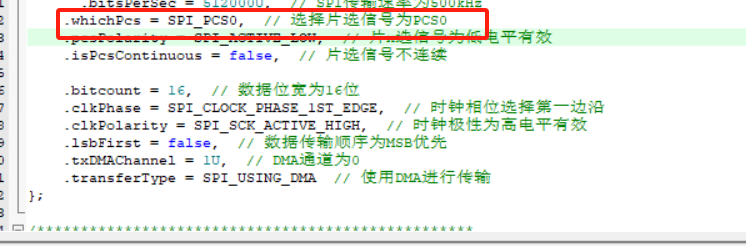

您好这个现象是已经调整过这个了,已经启用的dma,这个sck的帧间隔是正常的,也是一整包数据发送。中间那个50微秒的间隔是发送第二包数据的间隔,是第二次一整包数据的间隔即while第二次循环,下面那个波形是tum进行反转我设置的是硬件触发,但是实际上似乎一整包数据传输完成后反应并没有那么及时

您好这个现象是已经调整过这个了,已经启用的dma,这个sck的帧间隔是正常的,也是一整包数据发送。中间那个50微秒的间隔是发送第二包数据的间隔,是第二次一整包数据的间隔即while第二次循环,下面那个波形是tum进行反转我设置的是硬件触发,但是实际上似乎一整包数据传输完成后反应并没有那么及时

波形是已经调整过的,现在的情况是失真比较严重,应该是信号没有对齐,波形上中间的一段低电平不是发送中产生的,是我一整包数据发送完在发送第二包的时候有一段间隔,已经启用的dma,另外结束tmu的触发也是设置的硬件触发,跟spi的也对不上

波形是已经调整过的,现在的情况是失真比较严重,应该是信号没有对齐,波形上中间的一段低电平不是发送中产生的,是我一整包数据发送完在发送第二包的时候有一段间隔,已经启用的dma,另外结束tmu的触发也是设置的硬件触发,跟spi的也对不上

配置为0后,每一个字节的数据的会这样,每一整包的数据50ms依旧存在,这样配置似乎sck的整体频率就不对了

配置为0后,每一个字节的数据的会这样,每一整包的数据50ms依旧存在,这样配置似乎sck的整体频率就不对了 是的示波器的2是LRCLK,1是sck,因为产生严重的失真,猜测就是一个是LRCLK和sck的响应偏移太大,另外就是每一包数据间隔太长导致不停偏移

是的示波器的2是LRCLK,1是sck,因为产生严重的失真,猜测就是一个是LRCLK和sck的响应偏移太大,另外就是每一包数据间隔太长导致不停偏移 意思是这个没有影响?只要下一包的LRCLK根sck没有偏移就可以?我

意思是这个没有影响?只要下一包的LRCLK根sck没有偏移就可以?我