MCAL CddUart 模块关于Interrupt模式下使能FIFO优化分析

-

问题影响MCAL版本

所有使用UART 硬件IP的 MCAL CddUart。

TX使能FIFO的优化

问题描述

TX在Interrupt模式下未使能TX FIFO,会连续进入TX Empty 中断,中断响应次数过于频繁,代码运行效率下降,且会长时间进入中断服务,影响其他模块进入中断(比如WDG模块,会导致Ptmr不能及时进入中断进行喂狗导致复位风险。)

问题分析

CddUart使用UART作为硬件IP时(MC03,MD24)发送字符串的逻辑为:

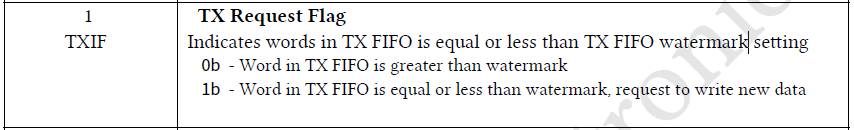

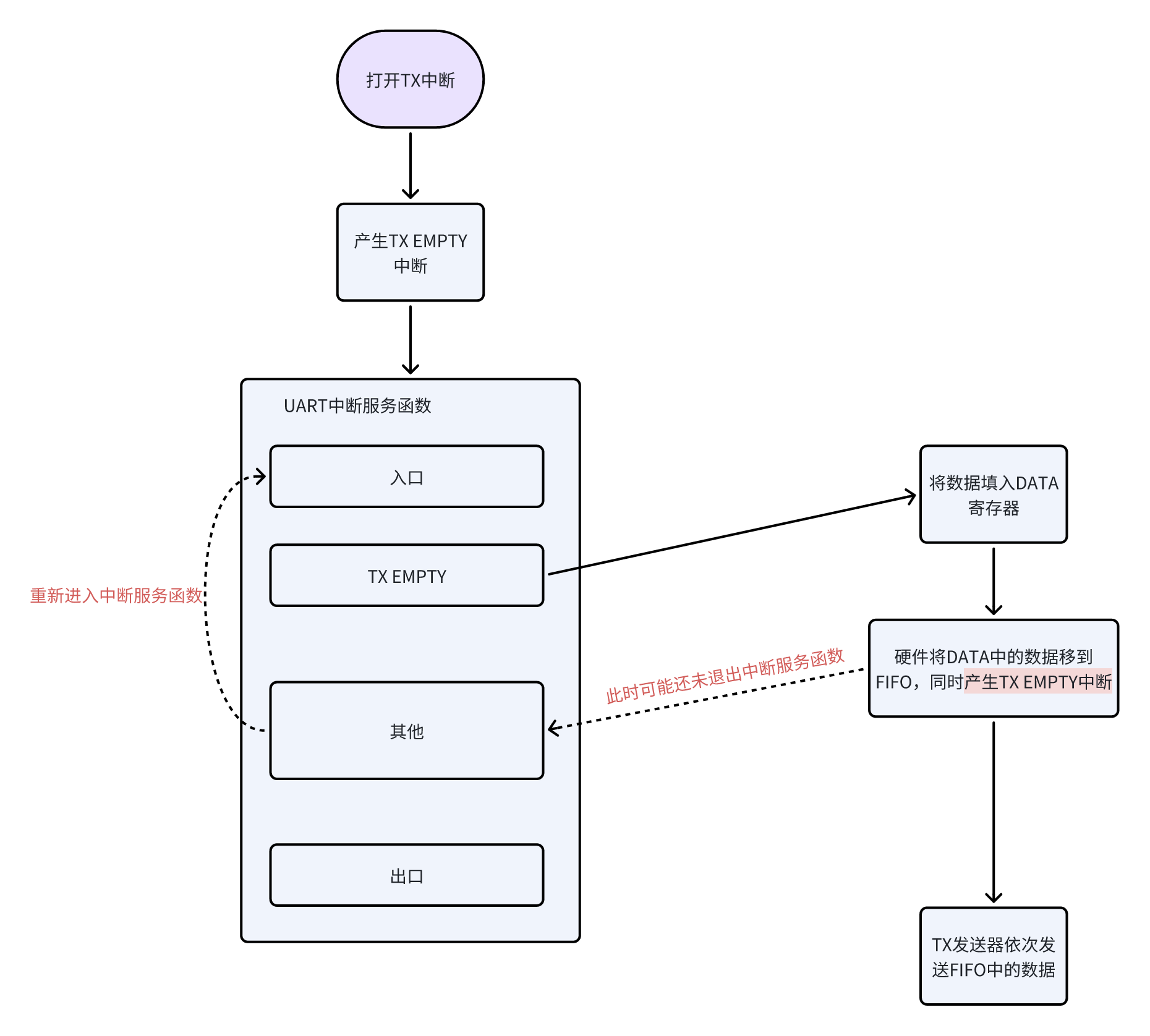

1、开启UART TX EMPTY中断以及发送器,此时当TX FIFO小于或者等于TX FIFO watermark时(如果没有使能FIFO,默认watermark为0),产生TX EMPTY,驱动根据在此中断里将需要发送的数据写入DATA寄存器。

![[TXIF]](https://yt-static-main.oss-cn-shanghai.aliyuncs.com/nodebb/242/34ce200a-3b45-43c6-b86a-ffd8f7c8f055.png)

2、当数据被填入DATA寄存器后,硬件会自动将DATA寄存器中的数据填入FIFO(无论是否使能FIFO)然后再通过发送器发送到总线上去。值得注意的是,当硬件将DATA寄存器填入FIFO时,便已经达到了触发TX EMPTY中断的条件,此时该数据也许还未来得及被发送器发送到总线上面。因此,TX EMPTY中断触发会非常频繁且快速,可能导致UART_Lld_IRQHandler还未退出,新的TX EMPTY中断就已经触发,导致一直进入该中断直到该字符串发送完成。

3、这种情况在使用PTMR定时喂狗的时候就会使UART一直抢占中断服务函数,导致无法及时进入PTMR中断服务函数进行喂狗。

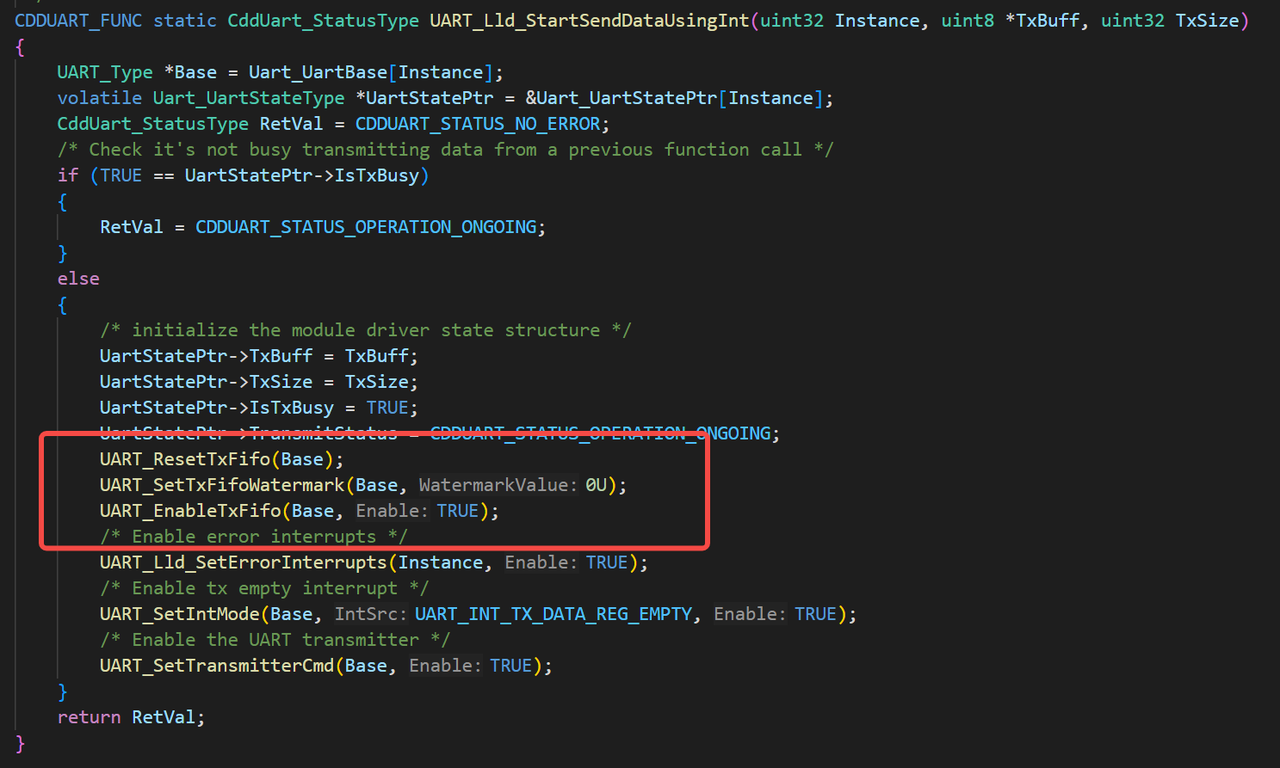

解决方案

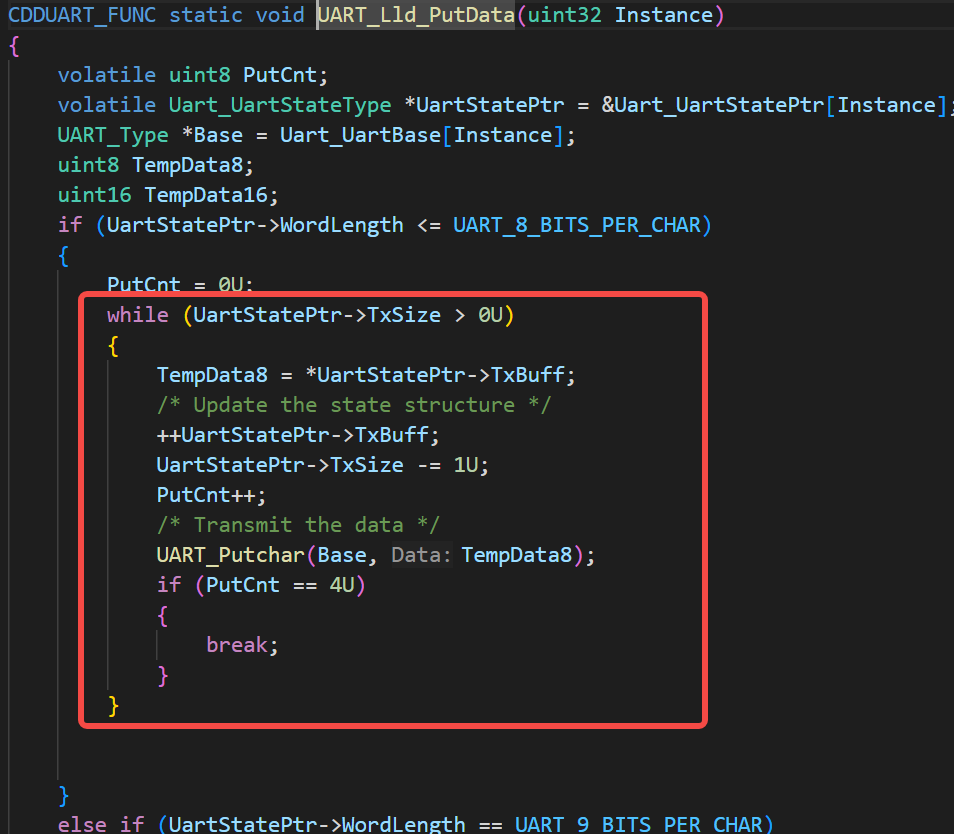

使能TX FIFO,Watermark设置为0,每次进入TX EMPTY中断时连续往DATA段输入4个字节(如果剩余字节不足4个字节,则将剩余字节全部填入。),这样减小了进入TX EMPTY中断的频率,提高了代码运行效率。

RX使能FIFO的优化

问题描述

使用UART自发自收(TX,RX短接),RX收到一个字节后出现Overrun错误

问题分析

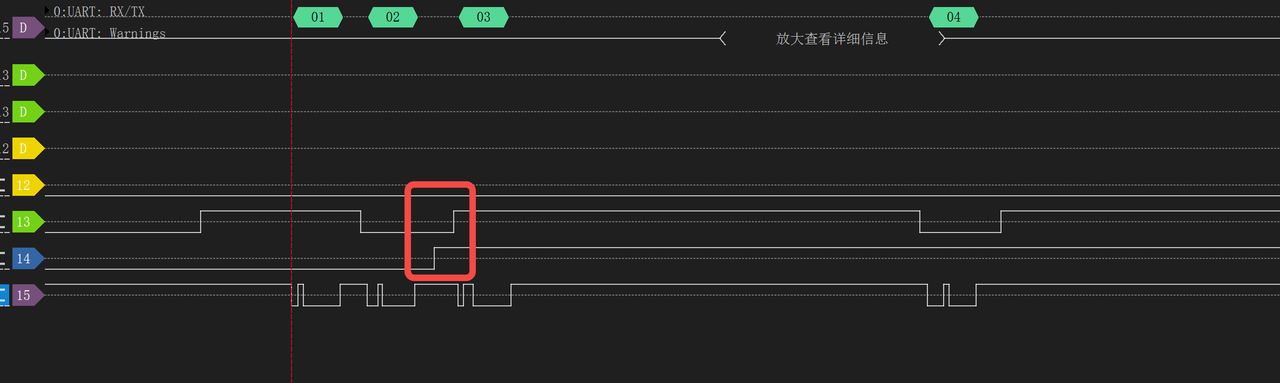

通道15为Uart 总线

通道14为 进入RX FULL中断触发GPIO翻转

通道13为 进入TX EMPTY中断触发GPIO翻转

可以看出TX因为频繁进入EMPTY中断,在RX收到第一个字节后置位RX FULL标志位,此时正在中断函数里,但由于RX FULL标志位是首先判断,此时已经错过了判断,当第二次进入中断时,已经接收到了第二个字节,产生了Overrun错误。

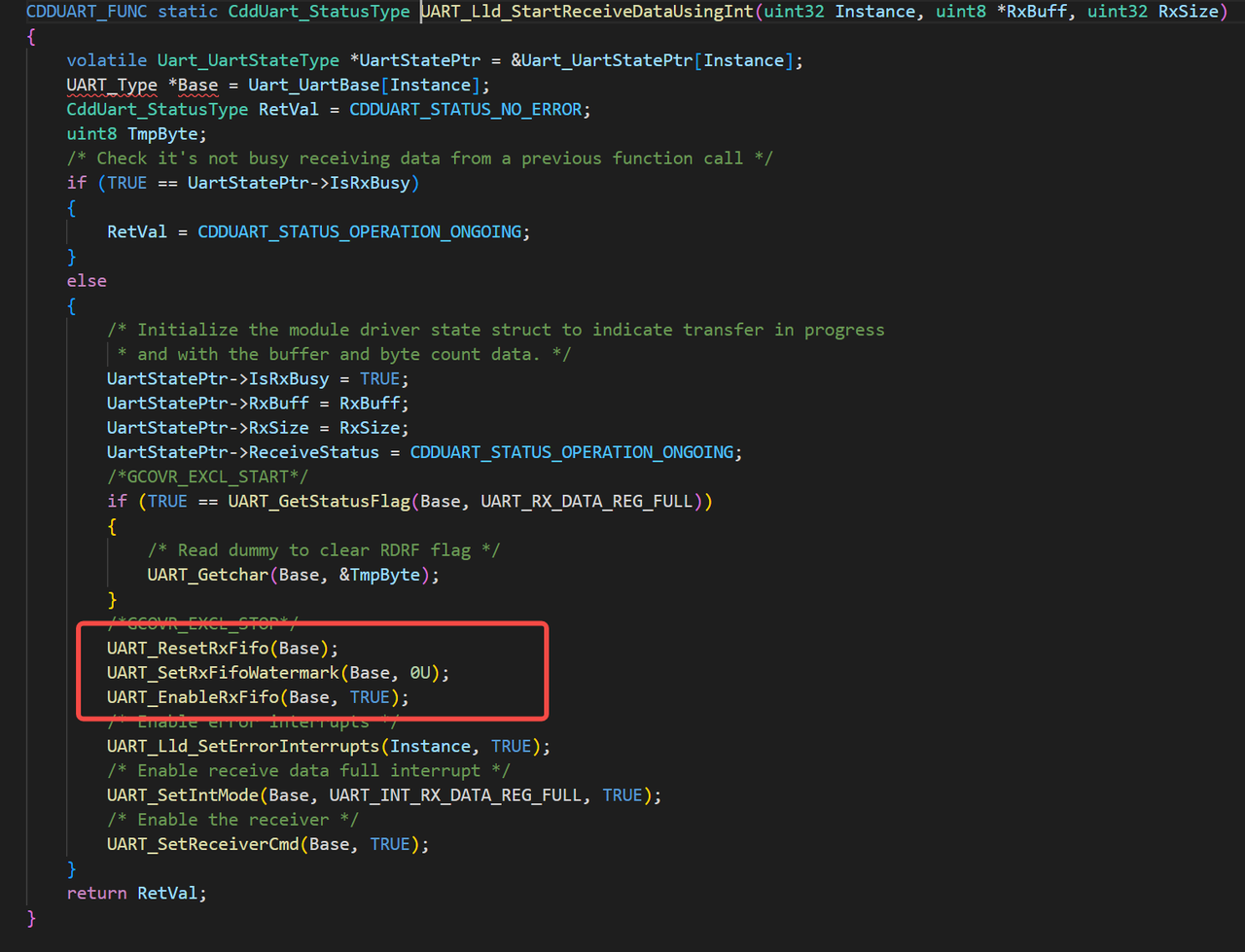

解决方案

开启RX FIFO,使其有一个缓冲区域,不会因为以上情况而导致出现RX Overrun错误。

-

J jiankang_wang 在 中 引用了 这个主题

快速上手云途开发生态

发帖前请查看

帮助改进和优化YT CONFIG TOOL,有机会抽取YTM32B1ME0 EVB哦...